A look under the hood of Nvidia’s Parker SoC

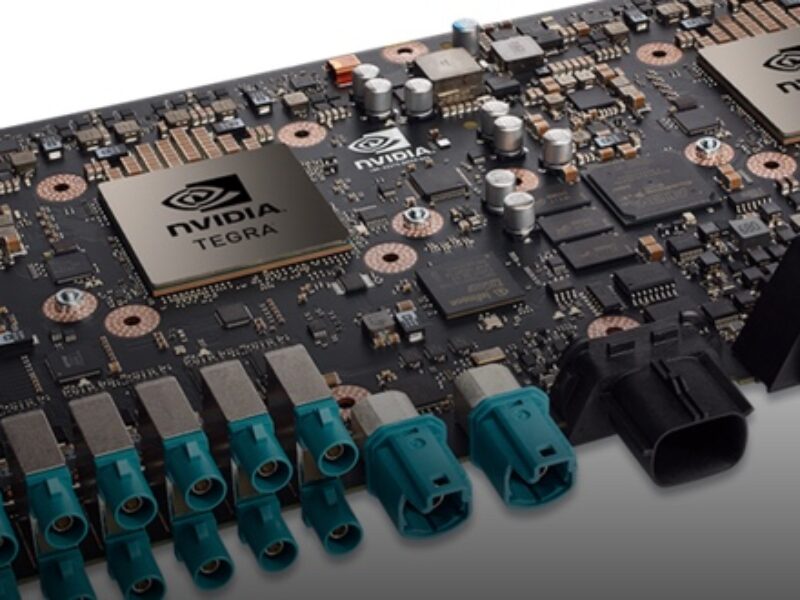

According to Nvidia, Parker supports features that currently belong to the most talked about topics in the automotive electronics realm: Deep learning, hardware-level virtualization, a hardware-based safety engine for reliable fault detection and error processing and a range of I/O ports for integration into the car’s electronic ecosystem. The Parker is built around Nvidia’s highest performing Pasal GPU architecture and the latest generation of Nvidia’s Denver CPU architecture, which also is said to be extraordinarily power-efficient – the latter being crucial in cockpit applications where OEMs do not exactly love to admit any cooling system that generates acoustic noise such as blowers. The combination of Pascal and Denver delivers a computing performance up to 1.5 teraflops for self-driving AI systems utilizing deep learning schemes.

for sophisticated deep learning algorithms

Thanks to its CPU architecture that consists of two 64-bit Denver 2.0 cores paired with four 64-bit ARM Cortex A57 CPUs, the Parker system delivers 50 to 100% higher multicore CPU performance than other mobile processors. The Denver 2.0 CPU is a seven-way superscalar processor supporting the ARMv8 instruction set. It implements an improved dynamic code optimization algorithm plus additional low-power retention states for better energy efficiency. The interconnection between the two Denver cores and the Cortex A57 CPU complexes is achieved by means f a proprietary interconnect fabric.

Working in concert with equally Pascal-based supercomputers in the cloud, the software of Parker based self-driving cars can be updated continually. The same holds true information to improve the driving performance of the vehicle’s electronic driver. While already one Pascal GPU with its 256 cores has sufficient computing power to run deep learning inference algorithms for the self-driving capabilities, the system is also scalable. The Nvidia Drive PX 2 employs two Parker chips with two discrete Pascal GPU cores. This combo delivers an awesome performance of 24 trillion deep learning operations per second, running even complex inference algorithms.

With features such as a dual CAN interface, the Parker platform takes the needs of automotive electronics into account. In addition, it supports Gigabit Ethernet as the network technology of choice for audio and video data streams today and automotive backbones tomorrow. Compliance with the safety standard in charge for automated driving, ISO 26262, is achieved through hardware safety features like a safety engine that includes a dedicated dual-lockstep processor that can detect and process faults.

Since the autopilot electronics of automated vehicles needs to be able to literally “see” everything around the vehicle with its camera eyes, Parker can bot encode and decode video streams up to 4K resolution – at a stunning rate of 60 frames per second. Thus, carmakers can use higher resolution in-vehicle cameras for more detailed and accurate object detection as well as 4K display panels for rear-seat entertainment.

Related articles:

Nvidia builds connections to AI researchers

Nvidia computer as processing hub for self-driving cars

How will deep learning change SoCs?

If you enjoyed this article, you will like the following ones: don't miss them by subscribing to :

eeNews on Google News

If you enjoyed this article, you will like the following ones: don't miss them by subscribing to :

eeNews on Google News